## 2025 IEEE VLSI Review

서울대학교 전기정보공학부 박사과정 박현준

#### **Session 19 Frequency Generation**

Session 19는 PLL/DCO 아키텍처와 인젝션 기법의 정교한 설계를 전면에 내세운다. 공통분모는 (1) 인젝션·리타이밍·디지털 피드백의 결합으로 PN/지터를 근본적으로 낮추고, (2) 보정 의존도 최소화로 환경 변화와 빠른 채널 전환에 대응하며, (3) 면적·전력 최적화로실사용 모듈 통합성을 높였다는 점이다. 결과적으로 본 세션은 낮은 rms 지터, 높은 fractional spur 억제성능, 넓은 튜닝 범위, mW-급 전력과 소형 코어까지 아우르며, 차세대 5G/6G, UWB, 그리고 100-400 Gb/s급 SerDes가 요구하는 클록 품질과 통합성의 새로운기준선을 제시한다.

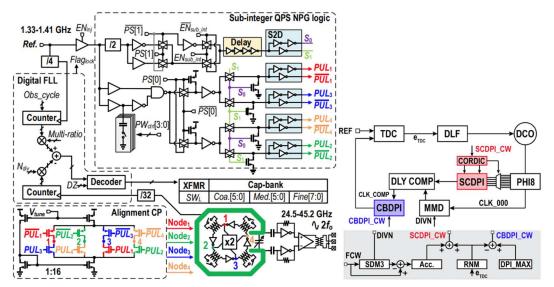

#19-1 본 논문은 28 nm HPC+에서 듀얼 인젝션·차동 타임-얼라인먼트를 결합한 광대역 ILCM(Injection-Locked Clock Multiplier)을 제안한다. 핵심은 (i) LC-series 듀얼-모드 QRO+ 엣지-컴바이닝 도블러 공설계로 자연 공진·배수 효율을 동시에 끌어올려 12.25-22.6 GHz(QRO) → 24.5-45.23 GHz(출력)의 초광대역을 확보하고, (ii) 폴디드 인덕터 기반 자기-플럭스 캔슬레이션과 원형 전원 가드링으로 LT·Q 변동을 억제해 PN을 저감, (iii) 동시에 상승/하강에지 정합(dual-node injection)으로 루프 대역폭(fBW)을 키워 링-기반의 PN 한 계를 극복한 점이다. 또한 서브-정수(0.5) 모드와 QPS-펄스 NPG로 N=9-32의 배수 범위를 지원해 입력 주파수 요구를 1.33-1.41 GHz(5.84%)로 축소한다. 그 결과, 39.5 GHz에서 32.83 fs\_rms(N=28), 저대역 25.4 GHz에서 40.55 fs\_rms(N=19, -42.6 dBc 서브-정수 스퍼)로 서브-50 fs 요구를 만족했고, 전 대역에서 FOM -255.7~-252.4 dB, FOM\_TA -277.7 dB(동급 최고)를 기록했다. 코어 면적 0.037 mm², 전력 22.8-26.8 mW, HRR ≈30 dBc로, 소형·저지터·광대역 mm-wave 클록을 배선 부담 없이 각 레인 인근에서 생성하려는 5G/6G· 초고속 SerDes 맥락에 적합함을 실측으로 입증한다.

[19-1] (좌) Top-level diagram of the proposed programmable timealignment ILCM with a detailed schematic of sub-integer quadraturephase-shifting pulse generator

[19-2] (우)Architecture of the proposed fractional-N ADPLL based on PRNM.

#19-2 본 논문은 40 nm CMOS에서 보정(calibration) 없이 분수 스퍼를 억제하는 PRNM(의사난수 위상 변조) 기반 ADPLL을 제안한다. 핵심은 (i) 두 개의 다른 구조 DPI—SCDPI(스위치드캡)로 위상 변조&분주 출력 재타이밍, CBDPI(차지-베이스드)로 역위상 복조를 동시 사용하여, (ii) 제어워드의 주기성(CW\_ideal)을 DPI 비선형성(NL\_DPI)과 의도적으로 분리하고 스펙트럼을 백색화(white-noising) 함으로써 fractional spur를 잡음저준위로 분산시키는 점이다. 이 방식은 DPD나 DTC 선형화 없이도 딜레이 범위/분해능 트레이드오프를 회피하며, 빠른 주파수 호핑·FMCW 레이다에 적합하다. 설계상 지연 보정으로 SCDPI 글리치를 제거하고, SCDPI·CBDPI의 위상 범위를 동일하게 맞춰 완전 복원을보장했다. 실측 결과, PRNM 미적용 시 근정수 채널에서 −60 dBc@48 kHz였던 스퍼가PRNM 적용 시 잡음저준위 아래(< −80 dBc 수준)로 사라졌고, 지터도 211.5 fs → 163.4 fs(−48.1 fs)로 개선되었다. 코어 면적 0.23 mm². 요컨대, "변조–복조"로 주기성·비선형성의결합을 끊어 스퍼를 백색화하는 아이디어가 보정 없는 저스퍼 ADPLL을 가능케 한 것이본 기여다.

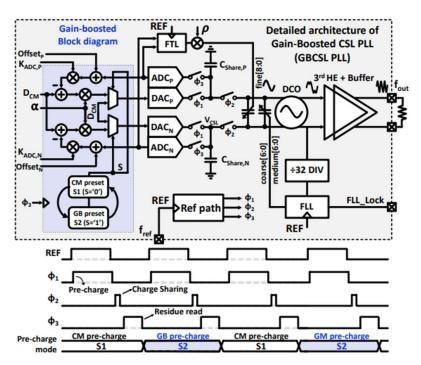

#19-3 28 nm 공정의 게인-부스팅 차지-셰어링 락킹(GB-CSL) PLL을 제안한다. 핵심 아이디어는, 차지-셰어링 단계에서 남는 잔류 전하를 온칩 플래시 ADC로 읽어 디지털로 이득을 키운 뒤, 아주 작은 차지-셰어링 캐패시터를 통해 DAC로 LC 탱크에 다시 주입하는 것이다. 이렇게 하면 유효 주입 이득이 커져 루프 대역폭이 넓어지고(인-밴드 지터가 감소), 동시에 탱크에 가해지는 부하 변조가 거의 늘지 않아 스퍼가 억제된다. 더 나아가이 잔류값을 주파수 추적 경로의 적분 이득에 재활용해 미세 캐패시터 뱅크 보정까지 통합함으로써 레퍼런스/하프-레퍼런스 스퍼를 체계적으로 낮춘다. 회로는 클래스-F 계열 DCO(트랜스포머 결합, 고조파 강화)와 4비트 CSL 펄스 생성기로 구성되며, 공통모드 사전-충전과 게인-부스트 사전-충전을 교번시키면서 위상 지연/선행에 따라 디지털 프리셋을 가변한다. 측정 결과 31.5-36 GHz 범위에서 rms 지터 54 fs(ref 500 MHz), 레퍼런스 스퍼 -66 dBc(10 GHz 기준 정규화 -76 dBc), 하프-레퍼런스 -73 dBc를 달성했고, 전 대역에서 스퍼 < -62.3 dBc, 지터 < 58 fs를 유지했다. 전력 14.8 mW, 코어 면적 0.183 mm², 그리고 지터/통합 성능 지표도 최상위권을 기록했다. 요약하면, 잔류 전하를 디지털로 증폭해 소형 캐패시터로 다시 주입하는 CSL 강화로 루프 대역폭 확장과 스퍼 억제를 동시에 이룬 저전력 mm-Wave PLL이다.

[19-3] Top-level diagram of the proposed GB-CSL PLL with its corresponding timing diagram.

# 저자정보

### 박현준 박사과정 대학원생

● 소속 : 서울대학교

● 연구분야 : 수학

● 이메일 : spp098@snu.ac.kr

## 2025 IEEE VLSI Review

단국대학교 파운드리공학과 석사과정 조혁준

#### **Session 25 Advanced PLLs**

Session 25에서는 Fractional-N 기반 PLL을 주제로 총 4편의 논문이 발표됐다. 최근 PLL 연구는 전력 소모를 고려하면서도 50fs 이하의 초저지터(ultralow jitter)와 -60dBc 이하의 스퍼(spur) 달성을 목표로 활발히 진행되고 있다. 본 리뷰에서는 그중 digital-to-time converter(DTC)를 기반으로 한 2편의 논문을 중점적으로 살펴보고자 한다.

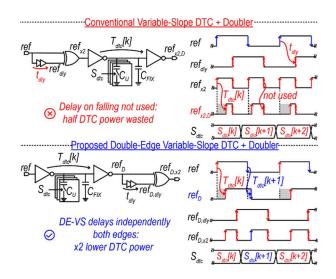

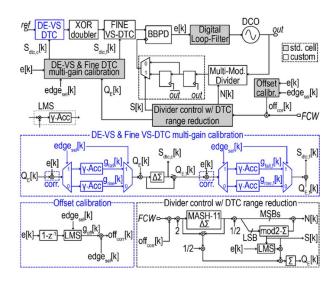

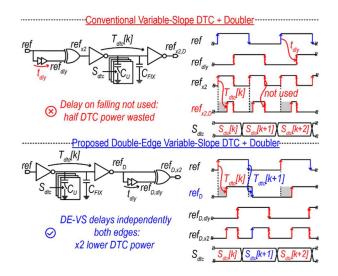

#25-2 본 논문은 밀라노 공과대학교에서 발표된 논문으로, DTC가 본질적으로 갖는 잡음 -선형성-전력 간 상충 관계에 초점을 맞췄다. 일반적으로 DTC 기반 PLL에서는 지터 (iitter)를 줄이기 위해 기준 주파수를 높이는 방식을 사용하지만, 이 경우 DTC의 동작 주 파수와 전력 소모가 증가하는 명확한 한계가 존재한다. 이를 해결하기 위해 논문은 '이중 엣지 가변 기울기 DTC(DE-VS DTC)'라는 새로운 구조를 제안한다. 기존 방식은 기준 신호 를 XOR 처리해 주파수를 두 배로 만든 뒤, 그 결과에서 지터가 심한 하강 엣지를 제거 하고 상대적으로 깨끗한 상승 엣지만을 DTC 보정에 활용한다. 반면 제안된 구조는 DTC 를 XOR 게이트 이전 단계에 배치해, 깨끗한 기준 신호의 상승 엣지와 하강 엣지를 모두 선제적으로 보정한다. 즉, 기존에 버려지던 하강 엣지까지 활용함으로써 DTC의 전력 소 모를 줄이는 것이 핵심 아이디어다. 제안된 PLL의 전체 회로(그림 2)는 정밀도를 극대화 하기 위한 계층적 DTC 구성과, DE-VS DTC에서 발생하는 불일치 문제를 해결하는 보정 루프를 포함한다. 계층적 구조에서는 DE-VS DTC가 넓은 시간 범위를 coarse하게 조정하 고, fine VS-DTC가 좁은 시간 범위를 세밀하게 조정해 넓은 조정 범위와 높은 해상도를 동시에 달성한다 또한 DE-VS DTC는 PVT 변동에 따라 오프셋 및 상승/하강 엣지 경로 간 이득 불일치가 발생할 수 있다. 논문은 이를 보완하기 위해 두 가지 기법을 도입했다. 첫 째, 연속된 위상 오차의 상관관계를 활용해 오프셋을 보상한다. 둘째, 이득 보정 루프를 통해 상승/하강 엣지를 구별하고, 각 경로의 위상 오차와 양자화 오차의 상관관계를 계 산하여 독립적으로 이득 값을 적용함으로써 두 경로를 일치시킨다. 제안된 PLL은 58.9fs 의 지터, -61.8dBc의 스퍼, 그리고 우수한 FoM을 달성하며 성능과 효율성을 동시에 입증 했다.

[그림 1] 제안된 DE-VS DTC

[그림 2] DE-VS DTC의 전체 회로도

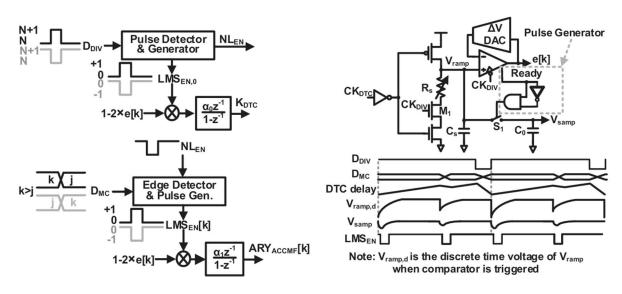

#25-3 본 논문은 홍콩과기대에서 발표한 논문으로, 높은 FoM 달성에 초점을 맞춘 DTC 기반 Fractional-N 샘플링 PLL을 제안한다. 이를 위해 DTC의 근본적인 문제인 비선형성을 해결하는 보정 기법과 위상 오차 검출 정밀도를 향상시키는 SPD를 추가했다. 제안된 PLL(그림 1)은 DTC 자체의 지연 및 지터(jitter) 기여도를 줄이기 위해 1차 DSM(ΔΣ Modulator)을 사용하며, 높은 성능 지수를 달성하는 데 초점을 맞췄다. 또한 넓은 동작범위와 높은 해상도를 동시에 확보하기 위해, 넓은 범위를 담당하는 4비트 Coarse DTC와 높은 정밀도를 담당하는 10비트 Fine VS-DTC로 구성된다. DTC 비선형성은 주로 Coarse DTC와 Fine DTC 간 지연 가중치 불일치에서 기인한다. 이를 해결하기 위해 논문은 Gated-LMS 보정 기법을 도입했다. 이 기법은 오류가 발생하는 Coarse DTC 코드 변경 시점만 포착해 보정 회로의 LMS 활성화 신호를 생성하고, 위상 오차와의 상관관계를 계산

해 전체 DTC 이득을 조정한다. 더 나아가 Coarse DTC 코드의 지연 가중치를 직접 보정해 선형성을 확보했다. 초기 구동 시에는 보조 DTC를 사용해 빠르게 초기값을 설정한 뒤, 이후에는 보조 DTC 전원을 차단하여 전력 효율을 높였다. SPD 구조에서 LMS 보정을 위해서는 위상 오차의 부호를 정확하게 얻어 내야 한다. 하지만 비교기 기반 방식은 킥백(kickback) 노이즈를 차단하기 위한 단위 이득 버퍼가 필요하다. 그러나 이 방식은 추가적인 전력 소모와 신호 진폭 감소라는 단점을 가진다. 이에 SPD 내부에서 신호 진폭이감소하기 전 단계인 1단 샘플러 출력에서 직접 비교를 수행해 정확도를 높였다. 동시에 2단 샘플러를 도입해 SPD 출력단과 비교기를 물리적으로 격리함으로써 킥백 노이즈 영향을 차단하고, 버퍼를 제거한다. 그 결과 제안된 PLL은 -257.4dB라는 매우 높은 FoM을 달성했다.

[그림 1] 제안된 fractional-N PLL

[그림 2] 제안된 Gated-LMS-based gain and nonlinearity calibration과 제안된 SPD

## 저자정보

### 조혁준 석사과정 대학원생

● 소속 : 단국대학교 파운드리공학과

● 연구분야 : Biomedical Circuits

● 이메일 : sdi5236@dankook.ac.kr

● 홈페이지: https://sites.google.com/dankook.ac.kr/acs-lab

## 2025 IEEE VLSI Review

고려대학교 전기전자공학과 박사과정 한창우

#### **Session 11 High-Performance Oscillators**

이번 VLSI 2025의 Session 11에서는 고성능 발진기(High-Performance Oscillator) 기술을 중심으로 총 5편의 논문이 발표되었다. 각 논문은 고주파 대역에서의 위상잡음 저감, 전력 효율 향상, 안정적인 동기화 구조, 초저전력 IoT 응용, MEMS 기반 초고안정성 발진기등 다양한 접근을 통해 차세대 발진기의 설계 방향을 제시하였다. 특히 멀티코어 VCO의소형화 및 저잡음 구현, MEMS 공진기를 활용한 Quartz 대체 가능성 입증, 초저전력 크리스털 발진기의 온도 보상 설계, 빠른 기동 속도를 달성한 injection 기반 발진기 등 회로 구조 혁신과 응용 확장성이 강조되었다.

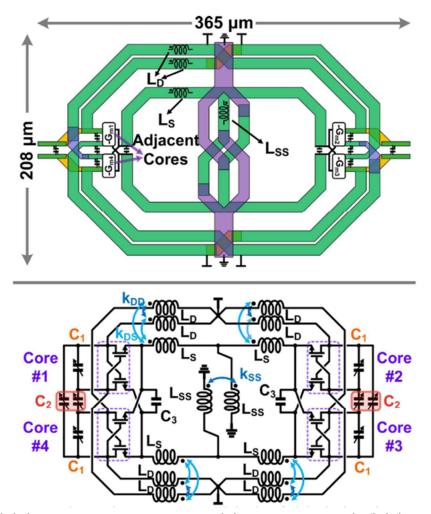

#11-2 본 논문은 Fudan University와 University of Macau에서 발표한 연구로, 28nm CMOS 공정 기반의 14.7~20.2GHz Quad-Core VCO를 구현하여 기존 멀티코어 발진기의 한계를 극복한 내용을 다룬다. 멀티코어 VCO는 위상잡음을 개선할 수 있으나, 코어 간주파수 불일치나 동기화 효율 저하로 인한 위상잡음 열화 문제가 발생한다. 이를 해결하기 위해 본 연구는 Folded Circular Transformer 구조를 제안하였다. 이 구조는 자기 결합과 전기 결합을 동시에 활용해 네 개의 발진 코어를 강력하게 동기화하고, 차동 모드 (DM)와 공통 모드(CM)에서 모두 높은 Q 인자를 확보한다. 특히 내부 Tail Coil을 통해 열잡음 업컨버전을 억제하고, 위상잡음을 1MHz offset에서 10dB 개선하였다. 또한 CM 공진의 임피던스가 기존 구조 대비 80% 증가하고 Q가 20% 향상되어 flicker noise 억제에 기여한다. 실리콘 검증 결과, 해당 VCO는 14.7~20.2GHz에서 동작하며, 전력 소모는 4.9~5.3mW, 칩 면적은 0.06mm²에 불과하다. 측정된 성능은 FoMA 203.4 dBc/Hz, FoMT 201.1 dBc/Hz로, 기존 동급 멀티코어 VCO 대비 30% 더 소형화되면서도 경쟁력 있는 위상잡음을 달성하였다. 본 연구는 소형화·저전력·저잡음을 동시에 만족하는 멀티코어 VCO 설계 전략을 제시하며, 차세대 고주파 응용에 적합한 아키텍처임을 입증했다.

[그림 5] 제안된 Folded Circular Transformer 기반 Quad-Core VCO의 레이아웃 및 등가 회로도

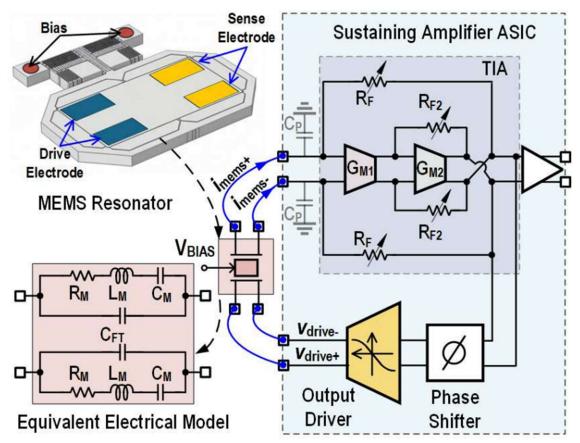

#11-3 본 논문은 University of Illinois와 Stanford University에서 발표한 연구로, 65nm CMOS 기반의 MEMS 발진기를 제작하여 Quartz 대체 가능성을 보여주었다. MEMS 공진 기는 집적성, 소형화, 저전력의 장점이 있으나, 높은 모션 저항(RM  $\sim M\Omega$ )과 피코암페어수준의 모션 전류로 인해 안정적인 발진을 구현하기 어렵다. 본 연구는 이를 해결하기위해  $5M\Omega$  트랜스임피던스 증폭기(TIA)와  $360^\circ$  위상 시프터를 결합한 발진 루프를 설계하였다. TIA는 Cherry-Hooper 구조를 기반으로 초저잡음(81  $fA/\sqrt{Hz}$ )과 가변 이득 특성을 제공하여 MEMS 공진기의 신호 대 잡음비를 개선하였다. 또한 위상 시프터는 RC 기반 Polyphase Filter와 10-bit 위상 믹서를 이용해 정밀한 위상 조절을 가능하게 하여 Barkhausen 조건을 안정적으로 만족시킨다. 제작된 발진기는 Q=864k의 MEMS 공진기와결합되어 -90 dBc/Hz@10Hz offset의 위상잡음을 달성했으며, Modified Allan deviation은 1ppb 수준으로 측정되었다. 24시간 측정에서 장기 안정성이 입증되었고, 드라이브 전압 및 위상 조건 조절을 통해  $1/f^3\sim1/f^2$  잡음 특성을 제어할 수 있음도 확인되었다. 본 연구는 MEMS 기반 발진기의 초저잡음·초고안정성 구현을 보여주며, 장기적으로 Quartz를 대체할 수 있는 고성능 온칩 주파수 참조원의 가능성을 제시하였다.

[그림 6] 제안된 65nm CMOS 기반 MEMS 발진기의 블록 다이어그램

### 저자정보

#### 한창우 박사과정

● 소속 : 고려대학교 전기전자공학과

● 연구분야 : 차세대 반도체 소자 및 회로

• 이메일 : cwoo0105@naver.com

● 홈페이지: https://sites.google.com/view/kudclab